Introduced in 1972

[1] by

Signetics,

[2] the 555 is still in widespread use due to its low price, ease of use, and stability. It is now made by many companies in the original

bipolar and in low-power

CMOS. As of 2003, it was estimated that 1

billion units were manufactured every year.

[3] The 555 is the most popular integrated circuit ever manufactured

HISTORY:

In 1962, Camenzind joined PR Mallory's Laboratory for Physical Science in

Burlington, Massachusetts.

[3] He designed a

pulse-width modulation (PWM) amplifier for audio applications,

[6] but it was not successful in the market because there was no power transistor included. He became interested in tuners such as a

gyrator and a

phase-locked loop (PLL). He was hired by Signetics to develop a PLL IC in 1968. He designed an oscillator for PLLs such that the frequency did not depend on the power supply voltage or temperature. However, Signetics laid off half of its employees, and the development was frozen due to a recession.

[7]

Camenzind proposed the development of a universal circuit based on the oscillator for PLLs, and asked that he would develop it alone, borrowing their equipment instead of having his pay cut in half. Other engineers argued the product could be built from existing parts, but the marketing manager bought the idea. Among 5xx numbers that were assigned for analogue ICs, the special number "555" was chosen.

[3][7]

Camenzind also taught circuit design at his nearby university

[which?] in the morning, and went to the

Northeastern University to get the master's degree at night. The first design was reviewed in the summer of 1971. There was no problem, so it had gone to the layout design. A few days later, he got the idea of using a direct resistance instead of a constant current source, and found that it worked. The change decreased the required 9 pins to 8, so the IC could be fit in an 8-pin package instead of a 14-pin package. This design passed the second design review, and the prototype was completed in October 1971. Its 9-pin copy had been already released by another company founded by an engineer who attended the first review and retired from Signetics, but they withdrew it soon after the 555 was released. The 555 timer was manufactured by 12 companies in 1972 and it became the best selling product.

Design

Internal schematic (bipolar version)

Internal schematic (CMOS version)

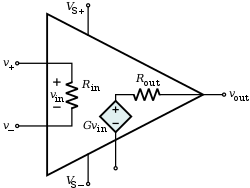

Depending on the manufacturer, the standard 555 package includes 25

transistors, 2

diodes and 15

resistors on a

silicon chip installed in an 8-pin mini dual-in-line package (

DIP-8).

[8] Variants available include the 556 (a 14-pin DIP combining two 555s on one chip), and the two 558 & 559s (both a 16-pin DIP combining four slightly modified 555s with DIS & THR connected internally, and TR is falling edge sensitive instead of level sensitive).

The

NE555 parts were commercial temperature range, 0 °C to +70 °C, and the

SE555 part number designated the military temperature range, −55 °C to +125 °C. These were available in both high-reliability metal can (T package) and inexpensive epoxy plastic (V package) packages. Thus the full part numbers were NE555V, NE555T, SE555V, and SE555T. It has been hypothesized that the 555 got its name from the three 5

kΩ resistors used within,

[9] but Hans Camenzind has stated that the number was arbitrary.

[3]

Low-power versions of the 555 are also available, such as the 7555 and CMOS TLC555.

[10] The 7555 is designed to cause less supply noise than the classic 555 and the manufacturer claims that it usually does not require a "control" capacitor and in many cases does not require a

decoupling capacitor on the power supply. Those parts should generally be included, however, because noise produced by the timer or variation in power supply voltage might interfere with other parts of a circuit or influence its threshold voltages.

The connection of the pins for a DIP package is as follows:

| Pin | Name | Purpose |

|---|

| 1 | GND | Ground reference voltage, low level (0 V) |

| 2 | TRIG | The OUT pin goes high and a timing interval starts when this input falls below 1/2 of CTRL voltage (which is typically 1/3 VCC, CTRL being 2/3 VCC by default if CTRL is left open). More simply we can say that OUT will be high as long as the trigger is kept at low voltage. Output of the timer totally depends upon the amplitude of the external trigger voltage applied to this pin. |

| 3 | OUT | This output is driven to approximately 1.7 V below +VCC, or to GND. |

| 4 | RESET | A timing interval may be reset by driving this input to GND, but the timing does not begin again until RESET rises above approximately 0.7 volts. Overrides TRIG which overrides THR. (THR instead overrides TRIG on the LM555) |

| 5 | CTRL | Provides "control" access to the internal voltage divider (by default, 2/3 VCC). |

| 6 | THR | The timing (OUT high) interval ends when the voltage at THR ("threshold") is greater than that at CTRL (2/3 VCC if CTRL is open). Overrides TRIG on the LM555 |

| 7 | DIS | Open collector output which may discharge a capacitor between intervals. In phase with output. |

| 8 | VCC | Positive supply voltage, which is usually between 3 and 15 V depending on the variation. |

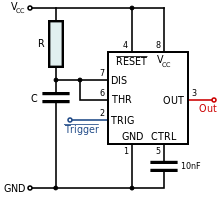

Pin 5 is also sometimes called the CONTROL VOLTAGE pin. By applying a voltage to the CONTROL VOLTAGE input one can alter the timing characteristics of the device. In most applications, the CONTROL VOLTAGE input is not used. It is usual to connect a 10 nF capacitor between pin 5 and 0 V to prevent interference. The CONTROL VOLTAGE input can be used to build an astable multivibrator with a frequency-modulated output.

Modes

The IC 555 has three operating modes:

- Bistable mode or Schmitt trigger – the 555 can operate as a flip-flop, if the DIS pin is not connected and no capacitor is used. Uses include bounce-free latched switches.

- Monostable mode – in this mode, the 555 functions as a "one-shot" pulse generator. Applications include timers, missing pulse detection, bounce-free switches, touch switches, frequency divider, capacitance measurement, pulse-width modulation (PWM) and so on.

- Astable (free-running) mode – the 555 can operate as an electronic oscillator. Uses include LED and lamp flashers, pulse generation, logic clocks, tone generation, security alarms, pulse position modulation and so on. The 555 can be used as a simple ADC, converting an analog value to a pulse length (e.g., selecting a thermistor as timing resistor allows the use of the 555 in a temperature sensor and the period of the output pulse is determined by the temperature). The use of a microprocessor-based circuit can then convert the pulse period to temperature, linearize it and even provide calibration means.

Bistable

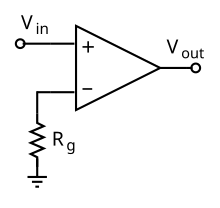

Schematic of a 555 in bistable mode

In bistable (also called

Schmitt trigger) mode, the 555 timer acts as a basic flip-flop. The trigger and reset inputs (pins 2 and 4 respectively on a 555) are held high via

pull-up resistors while the threshold input (pin 6) is simply floating. Thus configured, pulling the trigger momentarily to ground acts as a 'set' and transitions the output pin (pin 3) to Vcc (high state). Pulling the reset input to ground acts as a 'reset' and transitions the output pin to ground (low state). No timing capacitors are required in a bistable configuration. Pin 5 (control voltage) is connected to ground via a small-value capacitor (usually 0.01 to 0.1 μF). Pin 7 (discharge) is left unconnected, or may be used as an

open-collector output.

[11]

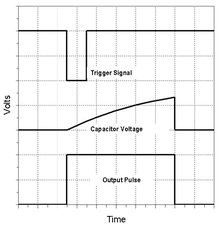

Monostable

Schematic of a 555 in monostable mode

The output pulse ends when the voltage on the capacitor equals 2/3 of the supply voltage. The output pulse width can be lengthened or shortened to the need of the specific application by adjusting the values of R and C.

[12]

The output pulse width of time t, which is the time it takes to charge C to 2/3 of the supply voltage, is given by

where t is in seconds, R is in

ohms (resistance) and C is in

farads (capacitance).

While using the timer IC in monostable mode, the main disadvantage is that the time span between any two triggering pulses must be greater than the RC time constant.

[13] Conversely, ignoring closely spaced pulses is done by setting the RC time constant to be larger than the span between spurious triggers. (Example: ignoring switch contact bouncing.)

Astable

Schematic of a 555 in astable mode

In astable mode, the 555 timer puts out a continuous stream of rectangular pulses having a specified frequency. Resistor R1 is connected between VCC and the discharge pin (pin 7) and another resistor (R2) is connected between the discharge pin (pin 7), and the trigger (pin 2) and threshold (pin 6) pins that share a common node. Hence the capacitor is charged through R1 and R2, and discharged only through R2, since pin 7 has low impedance to ground during output low intervals of the cycle, therefore discharging the capacitor.

In the astable mode, the frequency of the pulse stream depends on the values of R1, R2 and C:

[14]

[14]

The high time from each pulse is given by:

and the low time from each pulse is given by:

where R1 and R2 are the values of the resistors in ohms and C is the value of the capacitor in farads.

The power capability of R

1 must be greater than

.

Particularly with bipolar 555s, low values of

must be avoided so that the output stays saturated near zero volts during discharge, as assumed by the above equation. Otherwise the output low time will be greater than calculated above. The first cycle will take appreciably longer than the calculated time, as the capacitor must charge from 0V to 2/3 of V

CC from power-up, but only from 1/3 of V

CC to 2/3 of V

CC on subsequent cycles.

To have an output high time shorter than the low time (i.e., a

duty cycle less than 50%) a small diode (that is fast enough for the application) can be placed in parallel with R

2, with the cathode on the capacitor side. This bypasses R

2 during the high part of the cycle so that the high interval depends only on R

1 and C, with an adjustment based the voltage drop across the diode. The voltage drop across the diode slows charging on the capacitor so that the high time is a longer than the expected and often-cited ln(2)*R

1C = 0.693 R

1C. The low time will be the same as above, 0.693 R

2C. With the bypass diode, the high time is

where Vdiode is when the diode's "on" current is 1/2 of Vcc/R1 which can be determined from its datasheet or by testing. As an extreme example, when Vcc= 5 and Vdiode= 0.7, high time = 1.00 R1C which is 45% longer than the "expected" 0.693 R1C. At the other extreme, when Vcc= 15 and Vdiode= 0.3, the high time = 0.725 R1C which is closer to the expected 0.693 R1C. The equation reduces to the expected 0.693 R1C if Vdiode= 0.

The operation of RESET in this mode is not well-defined. Some manufacturers' parts will hold the output state to what it was when RESET is taken low, others will send the output either high or low.

The astable configuration, with two resistors, cannot produce a 50% duty cycle. To produce a 50% duty cycle, eliminate R1, disconnect pin 7 and connect the supply end of R2 to pin 3, the output pin. This circuit is similar to using an inverter gate as an oscillator, but with fewer components than the astable configuration, and a much higher power output than a TTL or CMOS gate. The duty cycle for either the 555 or inverter-gate timer will not be precisely 50% and will change based off any load that the output is also driving while high (longer duty cycles for greater loads) due to the fact the timing network is supplied from the devices output pin, which has different internal resistances depending on whether it is in the high or low state (high side drivers tend to be more resistive).

Specifications

These specifications apply to the NE555. Other 555 timers can have different specifications depending on the grade (military, medical, etc.).

| Supply voltage (VCC) | 4.5 to 15 V |

| Supply current (VCC = +5 V) | 3 to 6 mA |

| Supply current (VCC = +15 V) | 10 to 15 mA |

| Output current (maximum) | 200 mA |

| Maximum Power dissipation | 600 mW |

| Power consumption (minimum operating) | 30 mW@5V, 225 mW@15V |

| Operating temperature | 0 to 75 °C

|